- 全部

- 默认排序

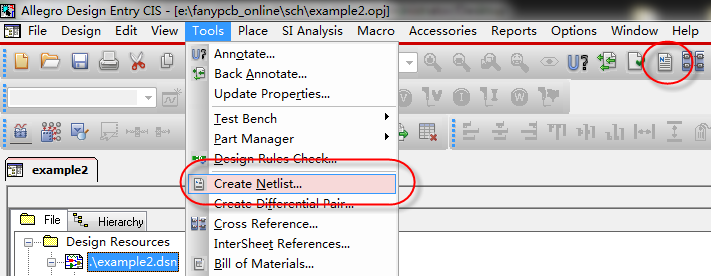

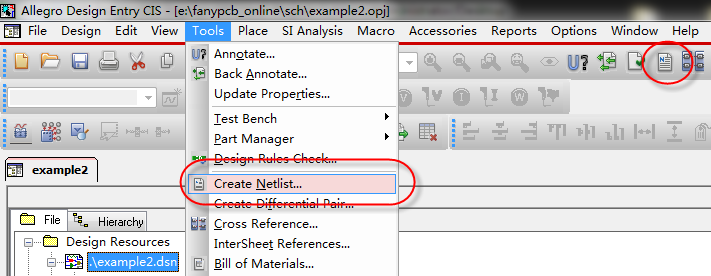

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-68所示; 图3-68 产生网表示意图第二步,弹出的Creat Netlist界面中,选择的是PCB Editor,产生Allegro的第一方网表,如图3-69所示; 图3-69 Allegro第一方网表参数设置示意图第三步,输入Allegro第一方网表需要注意下面几个

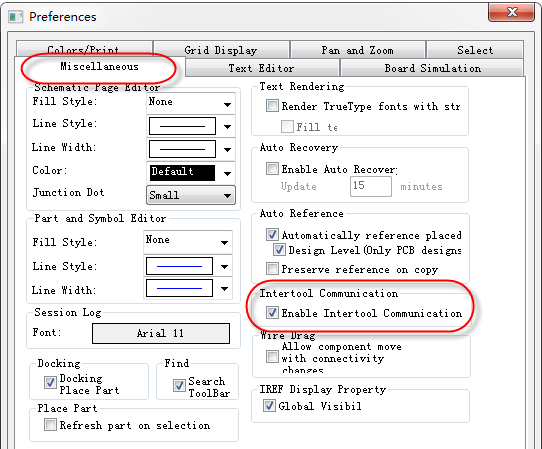

答:orcad与Cadence Allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是Allegro的第一方的网表,Allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

答:orcad产生Cadence Allegro的网表的操作步骤如下;第一步,选择原理图根目录,执行菜单Tools→Creat Netlist,或者是点击菜单栏上的图标,调出产生网表的界面,如图3-74所示; 图3-74 输出网表示意图第二步,弹出的输出网表界面中选择Other选项,来输出第三方网表,如图3-75所示,在Formatters栏中选择orTelesis.dll选项,上面的Part Value栏需要用PCB Footprint来代替,不然会产生错误;

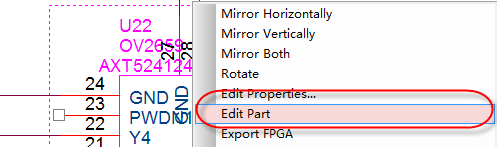

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36041): Duplicate Pin Name "GND" found on Package LCM0200CE1A0_3 , U22 Pin Number 25: SCHEMATIC1, 23.Camera (129.54, 50.80). Please renumber one of these.解决的办法如下所示:第一步,找到报错的器件U22,然后选中U22这个器件,点击右键,选择Edi

答:在使用Orcad软件输出Allegro第一方网表,出现如下错误:#1 ERROR(ORCAP-36022): Pin number missing from Pin "1" of Package TEST , P3: SCHEMATIC1, 05.RC5T620-System Power (15.60, 8.00). All pins should be numbered.解决的办法如下所示:第一步,找到管脚缺失的器件P3,然后选中P3这个器件,点击右键,选择Edit Part属性

答:我们在运用Orcad软件进行原理图的设计完成以后,需要通过Orcad软件进行物料清单的输出、然后对BOM清单进行整理。下面我们列一下,运用Orcad软件进行BOM清单输出的步骤如下:第一步,打开原理图主目录的界面,关闭掉其它的分界面,然后选中原理图的根目录,进行下一步的操作,如图3-90所示: 图3-90 原理图根目录选中示意图第二步,选中根目录以后,执行菜单命令Tools-Bill of Materials…命令,来进行BOM清单的输出,如图3-91所示: 图3-91

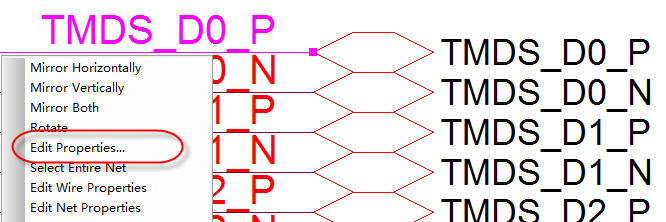

答:很多人很好奇,我们PCB文件可以添加差分信号属性,来进行走线,那原理图中可以对信号添加差分属性吗?这个当然也是可以的,下面就我们一步一步来给大家演示如何在原理图中进行差分属性的添加:第一步,首先需要在原理图中添加差分属性,选中差分信号的一根网络,然后点击鼠标右键,执行命令Edit Properties…,进行属性编辑,或者双击鼠标左键,也是一样的效果,如图3-99所示: 图3-99 信号差分属性编辑示意图第二步,进入信号属性编辑的界面,下边栏选中Schematic Ne

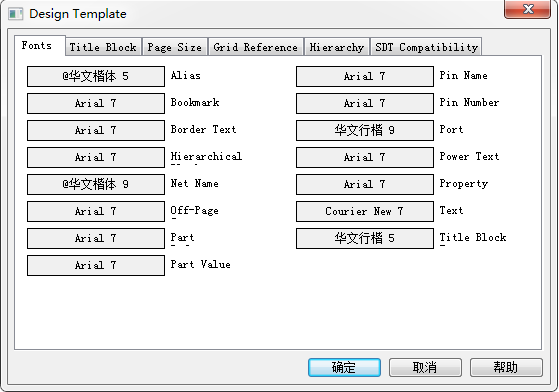

答:我们在运用Orcad进行原理图绘制时候,一般使用的都是默认的字体,用的最多的是就是网络标号的字体、位号的字体、封装属性的字体。当然使用默认字体是没有任何问题的,只是有时候我们将一些属性加以批示与标注,更加醒目这时就需要对其进行更改,一个一个去改费时费力,这里我们讲解下如何批量的去进行更改,具体操作的方法如下:第一步,首先打开原理图,对设计的模板进行更改,这样模板设定好了以后,原理图设计的内容都会根据模板来进行设定,执行菜单命令Options-Design Template,会弹出如图3-13

答:在设计原理图时,工程师们都喜欢在原理图中加上自己的独有标志或者是公司的logo,来表示这份原理图是该工程师绘制的或者是该公司的产品,这里我们就教一下大家,如何将公司的logo加入的原理图的Title Block中,具体的操作如下:第一步,Title block是一个全局的变量,存在于每一页的原理图中,我们需要在库里面的Title block加入图片,然后更新到原理图中;第二步,在当前设计的库Design Cathe路径下找到Title block的库,复制到本地的库路径下,才可以对其进行更改

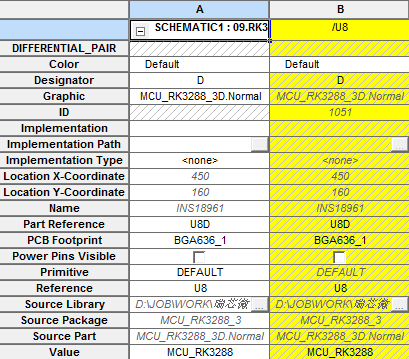

答:通常我们在编辑元件属性的时候会看到这样的界面,如图3-147所示,最直观的定义,白色的是“Instance”,黄色的是“Occurrence”。如果在“Root Schematic”放置器件会自动带有一个“Instance”和一个“Occurrence”,非“Root Schematic”放置器件只有“Instance”。为什么要分“Instance”、“Occurrence”?这种设置对设计是必要的吗?这个还要从Capture 的层次式原理图设计来讲。 图3-147 occurr

全站最新内容推荐

- 1加码技术,打破困境,PSPice电路仿真助你解锁职场新高度!

- 2简谈稳压二极管和普通二极管的区别

- 3贴片元件如何拆卸及焊接?

- 4盘点电子工程师必须了解的21个电路

- 5英伟达GB300芯片受阻,存在过热问题

- 6WARELEO李增原创H04课程大纲的安排课程中内容及工具及课程的重点学习办法的讲解

- 7WARELEO李增原创H03根据自己的关注知识点和所需要的知识来选择需要的图书包邮递

- 8WARELEO李增原创H02理工男生李老师的介绍从51单片机驱动到FPGA到仿真设计之路

- 9WARELEO李增原创H01信号电源完整性设计与HFSS射频天线设计仿真验证研修课程主题

- 10WARELEO李增:反射仿真的信号观察办法及时域串扰的仿真设置及观察技巧

扫码关注

扫码关注